**Understanding and Optimizing Tiered Memory and Storage Systems**

A Dissertation Proposal presented

by

**Tyler Estro**

to

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

**Doctor of Philosophy**

in

**Computer Science**

Stony Brook University

**Technical Report FSL-26-01**

**January 2026**

**Stony Brook University**

The Graduate School

Tyler Estro

We, the thesis committee for the above candidate for the

degree of Doctor of Philosophy, hereby recommend

acceptance of this thesis proposal

**Erez Zadok - Dissertation Advisor**

**Professor, Computer Science Department**

**Mike Ferdman - Chairperson of Dissertation Proposal**

**Associate Professor, Computer Science Department**

**Anshul Gandhi**

**Associate Professor, Computer Science Department**

**Carl Waldspurger**

**Consultant, Carl Waldspurger Consulting**

Abstract of the Dissertation Proposal

**Understanding and Optimizing Tiered Memory and Storage Systems**

by

**Tyler Estro**

**Doctor of Philosophy**

in

**Computer Science**

Stony Brook University

**January 2026**

Tiered memory and storage systems have become increasingly complex, combining heterogeneous devices across multiple layers to balance performance and cost. They underpin critical infrastructure, from operating system page caches and database buffers to large-scale AI training pipelines. These systems expose a vast configuration space, as many configurable parameters and design choices compound across tiers. As hierarchies deepen and workloads diversify, identifying optimal configurations has become both essential and increasingly difficult. Compute Express Link (CXL) further amplifies this challenge by adding a shared, byte-addressable memory tier accessible by multiple hosts, expanding the tiering space and requiring new techniques to effectively exploit it.

This thesis proposal has three thrusts. In the first thrust, we examined cache analysis trends and found that many techniques focus primarily on performance, analyze tiers in isolation, and overlook cost-performance trade-offs. To address these limitations, we implemented a multi-tier cache simulator that evaluates configurations across a broad range of parameters. Simulations on real-world traces revealed that cost-aware, multi-tier analysis can overturn common assumptions about device choice, hierarchy complexity, and policy effectiveness.

In the second thrust, we developed methods for efficiently exploring large tiered storage and memory configuration spaces. We designed a multi-stage frame-

work for analyzing cache miss-ratio curves that combines hash-based sampling, curve simplification, and knee detection, including a novel multi-knee detection technique “Z-Method”. To further support this exploration, we developed advanced interactive visualization techniques for analyzing large, high-dimensional configuration spaces. Lastly, we developed statistical performance models based on distribution fitting to better characterize and predict storage workload behavior.

In the third thrust, we propose two methods that apply CXL-based tiering to improve live virtual machine migration. The first method copies and transparently remaps guest memory to a shared memory device in a single pass, eliminating the need for dirty page tracking and retransmission. The second method partitions guest memory between DRAM and shared memory so that only DRAM-resident memory requires transfer. Together, these approaches aim to reduce migration time, blackout duration, and total data transferred compared to traditional migration methods.

It is our thesis that tiered memory and storage systems expose a vast configuration space with the potential for significant performance and cost optimizations. Fully realizing these benefits requires efficient techniques for both exploring and exploiting this space, particularly as the introduction of CXL shared memory adds new and powerful opportunities for tiering.

# Contents

|          |                                                                               |           |

|----------|-------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                           | <b>1</b>  |

| <b>2</b> | <b>Background and Motivation</b>                                              | <b>5</b>  |

| 2.1      | Live VM Migration Overview . . . . .                                          | 5         |

| 2.2      | Remote Direct Memory Access (RDMA) . . . . .                                  | 6         |

| 2.3      | Compute Express Link (CXL) . . . . .                                          | 8         |

| 2.4      | Thesis Statement . . . . .                                                    | 10        |

| <b>3</b> | <b>Related Work</b>                                                           | <b>11</b> |

| 3.1      | Live Migration Algorithms . . . . .                                           | 11        |

| 3.2      | RDMA-Based Migration . . . . .                                                | 12        |

| 3.3      | Shared Memory Migration . . . . .                                             | 12        |

| 3.4      | CXL Remote Memory and Tiering . . . . .                                       | 13        |

| <b>4</b> | <b>Desperately Seeking ... Optimal Multi-Tier Cache Configurations</b>        | <b>15</b> |

| 4.1      | Introduction . . . . .                                                        | 16        |

| 4.2      | Cache Analysis . . . . .                                                      | 18        |

| 4.3      | Multi-tier Cache Simulation . . . . .                                         | 19        |

| 4.4      | Evaluation . . . . .                                                          | 22        |

| 4.5      | Conclusion . . . . .                                                          | 27        |

| <b>5</b> | <b>Accelerating Multi-Tier Storage Cache Simulations Using Knee Detection</b> | <b>29</b> |

| 5.1      | Introduction . . . . .                                                        | 30        |

| 5.2      | Background . . . . .                                                          | 33        |

| 5.2.1    | Miss Ratio Curves (MRCs) . . . . .                                            | 33        |

| 5.2.2    | Knee-Detection Algorithms . . . . .                                           | 33        |

| 5.2.3    | Cliff Removal Techniques . . . . .                                            | 35        |

## CONTENTS

|           |                                                                                                        |           |

|-----------|--------------------------------------------------------------------------------------------------------|-----------|

| 5.2.4     | Evolutionary Algorithms: Population Initialization . . . . .                                           | 35        |

| 5.3       | Point Selection Techniques . . . . .                                                                   | 36        |

| 5.3.1     | Pre-Processing . . . . .                                                                               | 36        |

| 5.3.2     | Methods . . . . .                                                                                      | 37        |

| 5.3.3     | Post-Processing . . . . .                                                                              | 38        |

| 5.4       | Z-Method . . . . .                                                                                     | 39        |

| 5.4.1     | Design Concepts . . . . .                                                                              | 39        |

| 5.4.2     | Algorithm Description . . . . .                                                                        | 40        |

| 5.4.3     | Parameters . . . . .                                                                                   | 42        |

| 5.5       | Evaluation: Miss Ratio Curves . . . . .                                                                | 47        |

| 5.5.1     | Experimental Setup . . . . .                                                                           | 47        |

| 5.5.2     | Knee-Detection Algorithms . . . . .                                                                    | 48        |

| 5.5.3     | Multi-Tier MRCs . . . . .                                                                              | 51        |

| 5.6       | Evaluation: Population Initialization . . . . .                                                        | 56        |

| 5.6.1     | Experimental Setup . . . . .                                                                           | 57        |

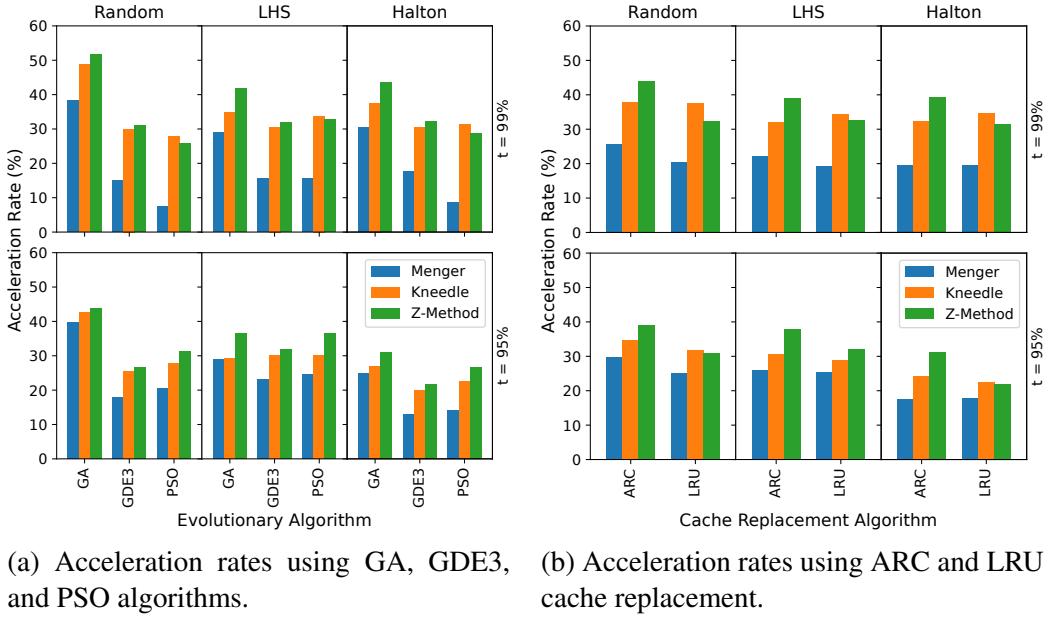

| 5.6.2     | Acceleration Rate . . . . .                                                                            | 58        |

| 5.7       | Conclusion . . . . .                                                                                   | 62        |

| <b>6</b>  | <b>Visual Analytics and Performance Modeling</b>                                                       | <b>63</b> |

| 6.1       | Advanced Interactive Visualizations . . . . .                                                          | 63        |

| 6.1.1     | ICE: An Interactive Configuration Explorer for High Dimensional Categorical Parameter Spaces . . . . . | 63        |

| 6.1.2     | PC-Expo: A Metrics-Based Interactive Axes Reordering Method for Parallel Coordinate Displays . . . . . | 67        |

| 6.1.3     | Into the Void: Mapping the Unseen Gaps in High Dimensional Data . . . . .                              | 67        |

| 6.2       | Distribution Fitting . . . . .                                                                         | 69        |

| <b>7</b>  | <b>Proposed Work</b>                                                                                   | <b>71</b> |

| <b>8</b>  | <b>Future Work</b>                                                                                     | <b>76</b> |

| <b>9</b>  | <b>Conclusion</b>                                                                                      | <b>78</b> |

| <b>10</b> | <b>Acknowledgments</b>                                                                                 | <b>80</b> |

# List of Algorithms

|   |                               |    |

|---|-------------------------------|----|

| 1 | Z-Method multi-knee detection | 40 |

|---|-------------------------------|----|

# List of Figures

|      |                                                                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | A high-level overview of data movement over RDMA. . . . .                                                                                        | 7  |

| 4.1  | Effects of an intermediate SSD tier . . . . .                                                                                                    | 23 |

| 4.2  | SSD Aging Effects . . . . .                                                                                                                      | 24 |

| 4.3  | Variation between vendor-reported specs and independently operated benchmarks . . . . .                                                          | 25 |

| 4.4  | Write-through vs. Write-back policy effect . . . . .                                                                                             | 26 |

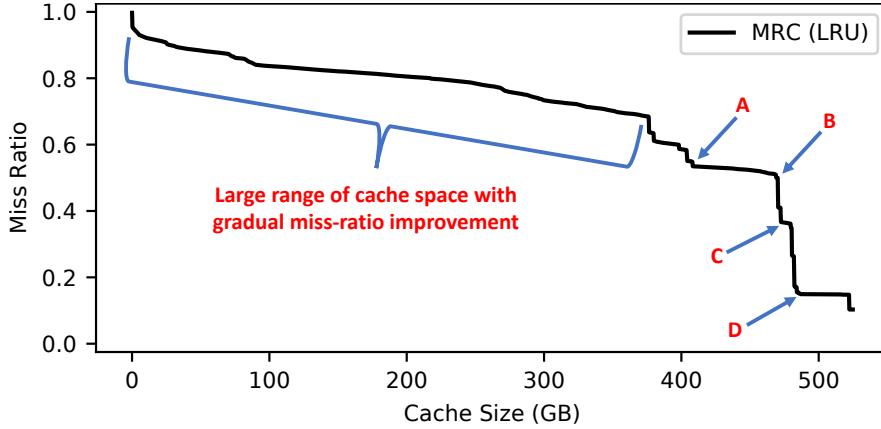

| 5.1  | MRC for trace w10, annotated to illustrate several key points . . . . .                                                                          | 31 |

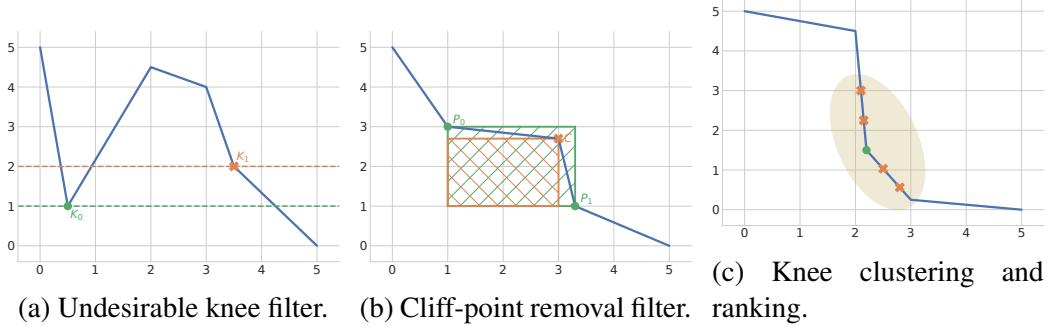

| 5.2  | Graphical representation of the post-processing methods . . . . .                                                                                | 38 |

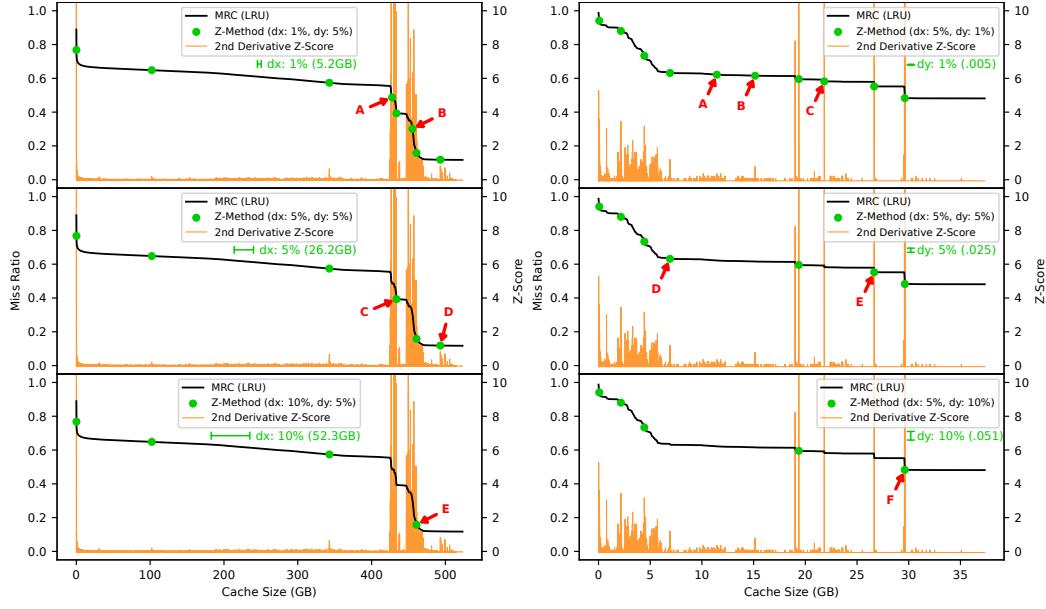

| 5.3  | Effects of Z-Method parameters $dx$ and $dy$ . . . . .                                                                                           | 42 |

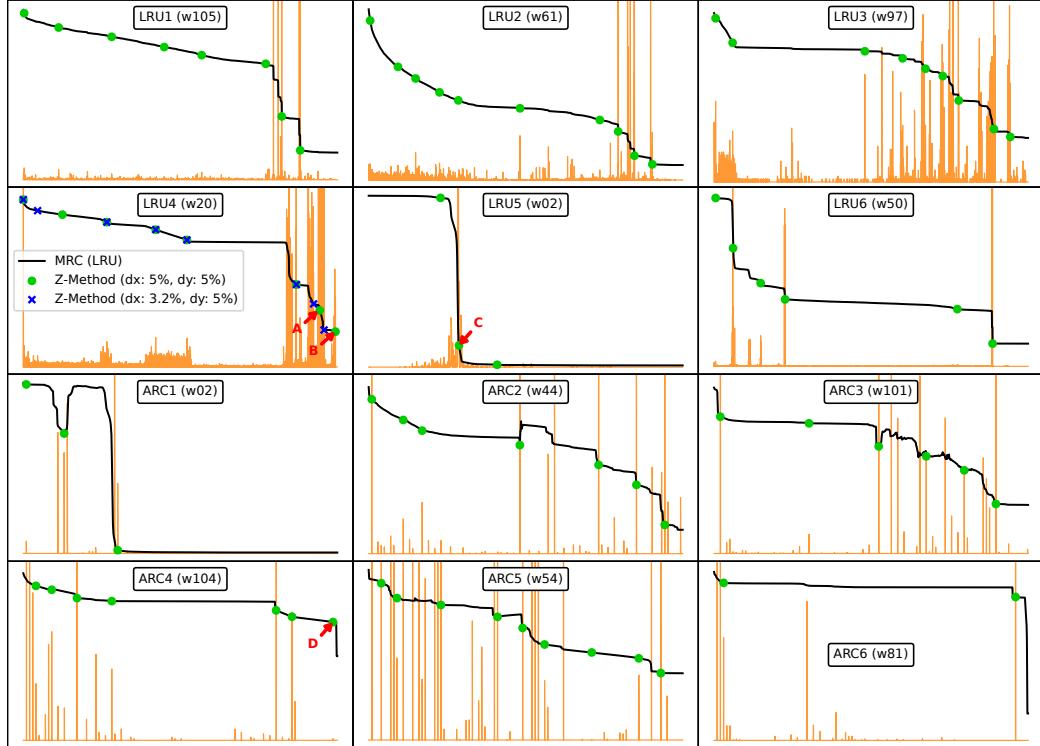

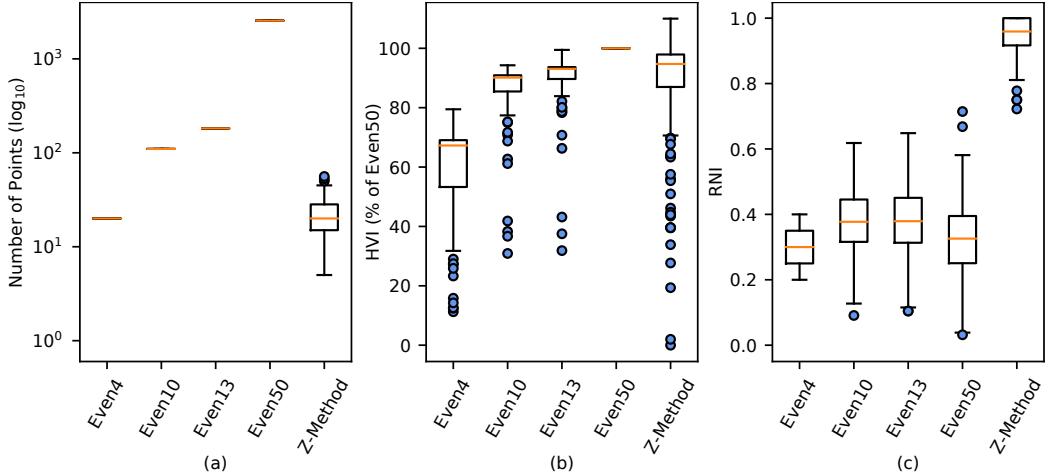

| 5.4  | Evaluation of Z-Method using ARC and LRU . . . . .                                                                                               | 45 |

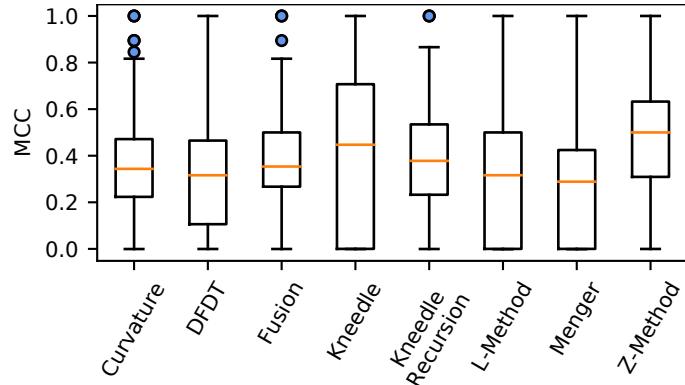

| 5.5  | An MCC evaluation of 8 knee detection algorithms using our optimized hyper-parameters . . . . .                                                  | 48 |

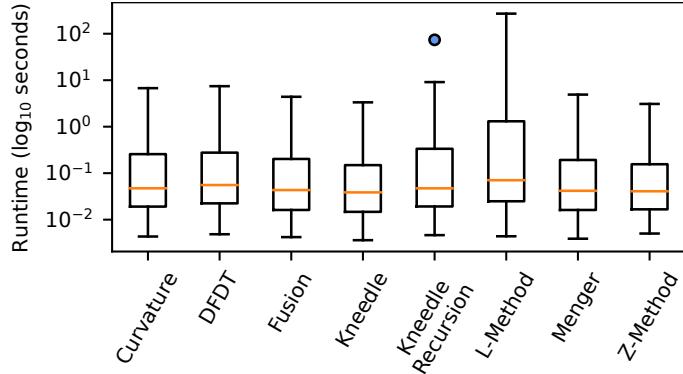

| 5.6  | Running times for 8 knee-detection algorithms . . . . .                                                                                          | 50 |

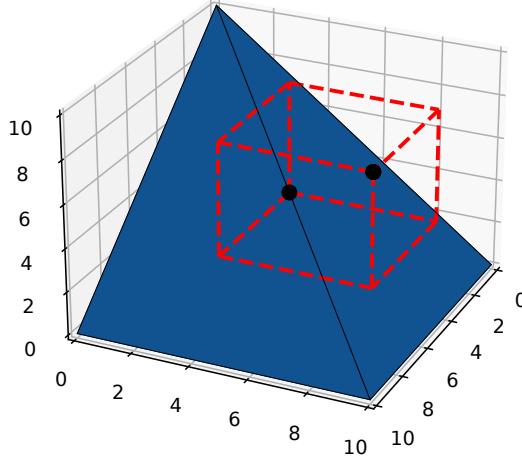

| 5.7  | An example of how the HyperVolume Indicator is calculated . . . . .                                                                              | 52 |

| 5.8  | Evaluation results of our framework using Z-Method across 2-tier ARC and LRU MRCs . . . . .                                                      | 54 |

| 5.9  | Examples of point selection on two-tier MRCs that highlight three different commonly observed scenarios . . . . .                                | 55 |

| 5.10 | The acceleration rate ( $\overline{AR}$ ) achieved using our multi-knee detection framework for population initialization vs. other techniques . | 60 |

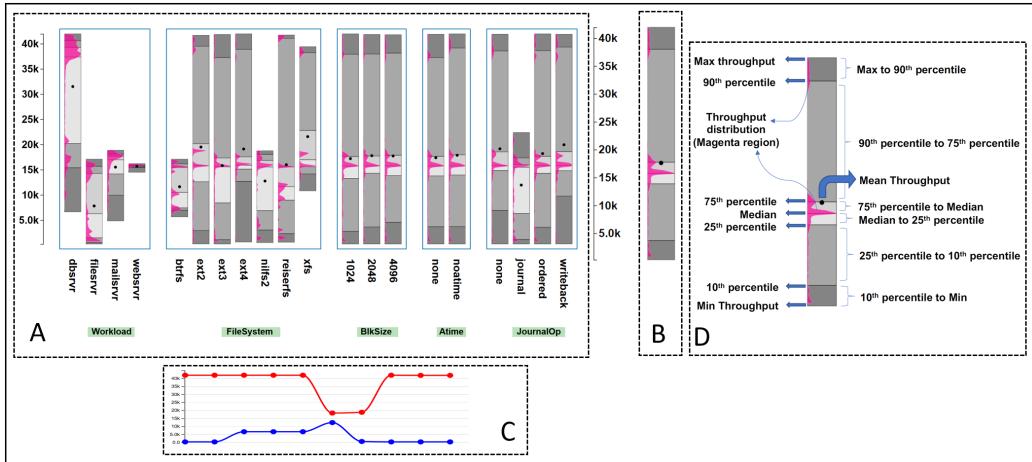

| 6.1  | Interactive Configuration Explorer (ICE) . . . . .                                                                                               | 64 |

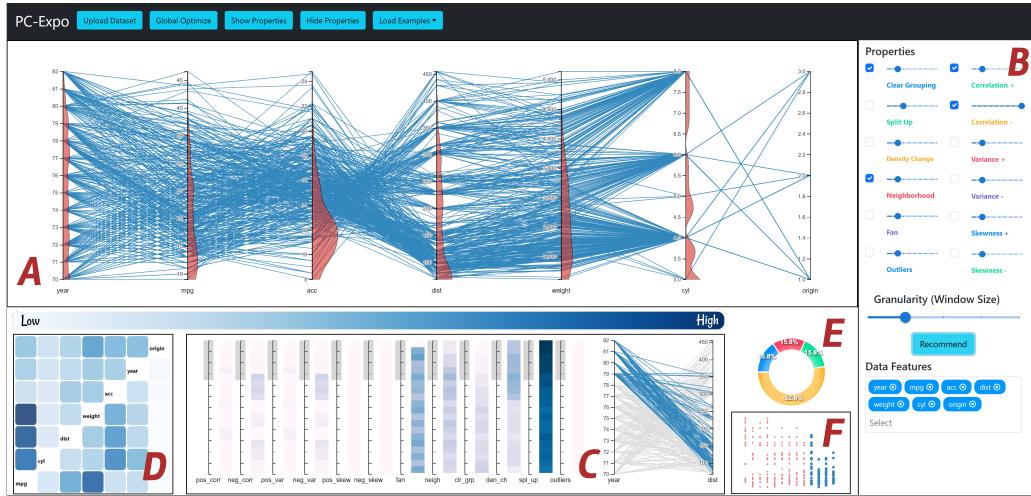

| 6.2  | PC-Expo: Parallel Coordinate Plot axes reordering framework . .                                                                                  | 66 |

| 6.3  | GapMiner visual interface . . . . .                                                                                                              | 68 |

# List of Tables

|     |                                                                                                |    |

|-----|------------------------------------------------------------------------------------------------|----|

| 4.1 | Device specifications and parameters . . . . .                                                 | 28 |

| 5.1 | Evaluation results of our framework using Z-Method across 2-tier<br>ARC and LRU MRCs . . . . . | 53 |

# Chapter 1

## Introduction

Modern storage and memory hierarchies have become increasingly complex, forming multi-tier systems comprising heterogeneous devices in a wide range of topologies. From operating system page caches to large-scale distributed systems, tiering is employed to improve performance while reducing total cost of ownership (TCO). Cloud providers often dynamically reconfigure memory and storage hierarchies to meet service-level objectives (SLOs), balance loads, or in response to hardware faults [164, 72, 49, 27, 28]. The configuration space for tiering systems is vast, spanning device types, number of tiers, tier capacities, and tiering management policies, each with tunable parameters that influence performance and cost [38]. To navigate this space effectively, techniques must be efficient in (i) identifying high-quality configurations and (ii) adapting quickly to changing locality and reuse behavior as workload access patterns vary over time [121, 147, 116, 10, 24, 152]. Within this evolving landscape, Compute Express Link (CXL) introduces a cache-coherent interconnect that allows multiple hosts to access a shared, byte-addressable memory tier [45]. CXL significantly complicates the tiering space by introducing this fundamentally new paradigm while enabling novel techniques to exploit its potential.

This work addresses two distinct challenges of tiering. The first is the efficient exploration of the complex design space in tiered systems to identify optimal configurations. The second is the effective implementation of tiering to fully realize its benefits in modern systems. Addressing both challenges is essential for achieving high performance while maintaining cost efficiency.

In the first thrust, to address the challenge of efficiently exploring the complex design space in tiered systems, we examined cache analysis trends and identified key limitations in existing evaluation techniques [38]. We found that past tech-

## CHAPTER 1. INTRODUCTION

niques often focused solely on performance, analyzed tiers in isolation, and ignored trade-offs such as cost versus performance. Current cache simulators were similarly restrictive, supporting only fixed hierarchies and limited metrics. We addressed these gaps by extending PyMimircache [155] to create a general  $n$ -level cache simulator capable of modeling arbitrary hierarchies, capturing both performance and cost, and enabling the analysis of trade-offs across multiple metrics. We uncovered surprising insights through simulations using real-world traces: (a) when total cost was held constant, lower-priced DRAM outperformed high-end DRAM by providing greater capacity; (b) aging SSDs reduced performance enough to favor simpler designs; and (c) write-back policies delivered up to  $6\times$  the throughput of write-through on identical hardware.

In the second thrust, we further addressed the challenge of efficient exploration by developing a framework to efficiently characterize multi-tier caches [37]. Miss-ratio curves (MRCs) are common analysis tools for evaluating cache performance, but generating them at fine granularity for every tier and configuration can be prohibitively expensive. Our approach focuses on identifying knee points in MRCs, where a small increase in cache size yields a disproportionately large drop in miss ratios, indicating promising candidates for further evaluation. The framework applies hash-based sampling [141], curve simplification [110], and adapts any single-knee detection algorithm to find multiple knee points [8, 117, 129]. In addition, we introduced a novel multi-knee detection algorithm, called Z-Method, that employs statistical outlier detection to identify points robustly and efficiently. We evaluated our framework using 106 diverse real-world workloads, and were able to reduce the number of simulations needed to find optimal two-tier hierarchies by  $5.5\times$  for ARC and  $7.7\times$  for LRU. We also applied our framework to seed the initial population of evolutionary algorithms that we used to optimize multi-tier cache configurations, achieving an overall convergence-acceleration rate of 34% across a broad range of configurations and datasets [37].

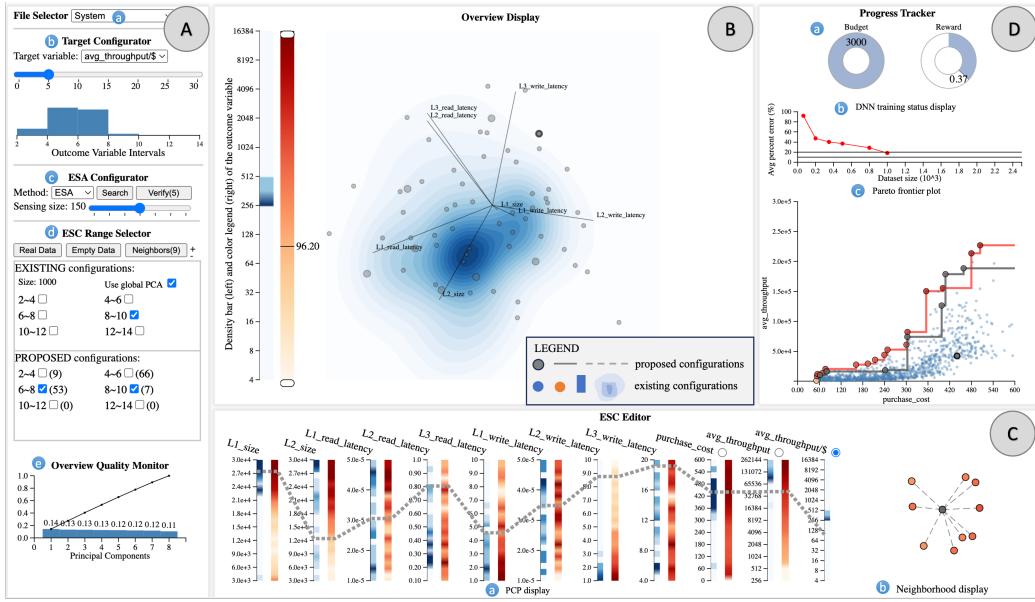

To further support exploration, we developed a set of advanced interactive visualizations designed to help analysts interpret large, high-dimensional configuration spaces. First, we created an interactive configuration explorer that allows users to examine how categorical design choices influence system behavior and to compare competing configuration families through guided visual analysis [132]. Second, we built a parallel-coordinate axes-reordering framework that enables users to uncover structural patterns and relationships across configuration parameters by automatically arranging axes to emphasize informative pairings [133]. Lastly, we introduced an empty-space analysis technique that identifies promising, previously unsampled configurations by detecting sparsely populated gaps in

## CHAPTER 1. INTRODUCTION

the design space that may contain high-value alternatives [163].

In addition to these visualization tools, we developed statistical models that apply distribution fitting to characterize storage workload behavior [140]. Through an extensive evaluation of real-world traces, we found that the two-phase Hyper-exponential provides the best empirical fit to storage workload distributions. This result enables substantially more accurate queuing models that provide performance predictions for cache and storage hierarchies.

In our third thrust, to address the challenge of effectively implementing tiering in modern systems, we propose to apply tiering to live virtual machine (VM) migration using CXL. Unlike traditional migration approaches that rely on repeated memory transfers and dirty page tracking [29], CXL enables multiple hosts to directly access the same byte-addressable memory region. We explore two designs: (1) a CXL-based migration mechanism that eliminates dirty tracking entirely and (2) a tiered-memory approach that reduces migration cost by placing part of the VM’s memory in shared CXL space. Both approaches aim to reduce total migration time, blackout duration, and data movement compared to state-of-the-art techniques such as RDMA.

The first proposal of this thesis is a new CXL-based migration mechanism implemented in QEMU. In this approach, the source machine performs a one-time copy of the VM’s memory from local DRAM into CXL memory while the VM continues executing. After each page is copied to CXL, the hypervisor transparently remaps the guest’s physical address pointer to point to CXL memory. As a result, all subsequent VM writes transparently go directly to CXL, and there is no need to track dirty pages. This eliminates the complexity and performance penalty of traditional dirty tracking mechanisms. Once all pages have been transferred to CXL, the destination host resumes the VM immediately from shared CXL memory, without waiting for memory to be copied to its local DRAM. From there, the destination may choose to migrate memory lazily into DRAM for performance, or continue executing from CXL.

The second proposal of this thesis is to implement memory tiering and the migration of tiered memory within QEMU. In this model, the guest VM’s memory is split between local DRAM and a shared CXL device. Since the CXL memory is shared and visible to both hosts, pages that reside in CXL require no data movement during migration. Only the portion of memory that is located in local DRAM must be transferred. This significant reduction in data movement directly translates to a much shorter total migration time. We also plan to evaluate hybrid methods, where local memory is migrated using traditional methods such as TCP or RDMA—to explore if there are scenarios where this is more optimal than pure

## *CHAPTER 1. INTRODUCTION*

CXL-based migration.

It is our thesis that tiered storage and memory systems expose a vast configuration space with the potential for significant performance and cost optimizations. Fully realizing these benefits requires efficient techniques for exploring and exploiting this space, particularly as the introduction of CXL shared memory and tiering adds new and powerful opportunities for tiering.

The rest of this thesis proposal is organized as follows: Chapter 2 provides additional background on live migration, RDMA, CXL, as well as motivation for this work. Chapter 3 reviews prior work relevant to live VM migration and CXL. Chapter 4 examines cache analysis techniques and introduces our multi-tier cache simulator. Chapter 5 presents our work on accelerating multi-tier storage cache simulations using knee detection. Chapter 6 presents interactive visualization tools and workload modeling techniques that support exploring and analyzing complex system design spaces. Chapter 7 presents our proposed work on CXL-based migration and tiered migration. Chapter 8 discusses future work outside of the scope of this thesis. Chapter 9 concludes the proposal and outlines future research directions. Chapter 10 acknowledges the contributions of collaborators, institutional support, and funding agencies.

# Chapter 2

## Background and Motivation

In this chapter, we provide background information relevant to live VM migration and describe our vision and motivations for applying CXL-based tiering to migration. We begin by describing the different live VM migration techniques. Then we give some background on RDMA and discuss how it is used for live VM migration. Lastly, we provide some background on CXL.

### 2.1 Live VM Migration Overview

Live VM migration involves transferring the VM state from the source machine to the target machine. Much of this state is the contents of the VM’s memory pages, which presents two main problems: (1) increasing memory sizes mean an increasingly large amount of data must be transferred to the target host, and (2) as the VM continues running, the memory contents at the source host continue to change. There are three primary paradigms for live-VM migration that have been developed to mitigate these issues: pre-copy, post-copy, and hybrid—described next.

The pre-copy technique comprises three phases. In the first phase, all of the VM’s memory pages are copied to the target machine while the VM continues to run on the source host. Pages can be dirtied by the workload on the source host during this time because the VM is still active. The second phase iteratively copies the dirtied pages until a stopping condition is met. The final stop-and-copy phase begins when this condition is met; the VM is paused on the source host, all remaining pages are copied to the target machine, and the hypervisor resumes VM execution on the target.

The post-copy technique takes the opposite approach. The minimum VM state required to resume execution is first copied to the target machine, and then VM execution is immediately resumed on the target without copying over any memory pages. Memory is then handled using demand paging, where page faults require transmission from the source machine. Several optimizations have been proposed to reduce the number of page faults, including active push, pre-paging, and Dynamic self-ballooning [26].

The third technique is a hybrid that combines both pre- and post-copy methods. The pre-copy portion runs for a single round, rather than the iterative approach used in traditional pre-copy. Some versions of this technique only copy over a fraction of the memory and storage, such as adaptive live VM migration [161]. After the pre-copy phase, the minimal VM state is copied to the target machine and VM execution is immediately resumed. Finally, the rest of the memory pages are handled using demand paging as in traditional post-copy.

All of the existing migration techniques have significant CPU, memory, storage, and network overheads. The migration process heavily degrades the performance of guest workloads and adversely affects the efficiency of the data center [26]. The overheads are typically classified as either blackout or brownout phases. A blackout phase occurs during traditional pre-copy, where VM execution is halted as the last dirty pages are copied over. A brownout phase refers to the time during migration while the VM is still active and performance is degraded. Brownout phases are particularly problematic, as they can significantly degrade performance for multiple minutes.

## 2.2 Remote Direct Memory Access (RDMA)

RDMA allows data to be transferred directly between the memory of two machines over a network without involving their operating systems or CPUs. RDMA provides low latency and high throughput by bypassing the CPU, making it ideal for applications requiring rapid access to remote memory, such as distributed databases, big data analytics, and cloud services. While this technology offers tangible benefits, RDMA still has at least three *architectural limitations*.

The first challenge with RDMA is the complexity and overhead of its memory management protocols. Before using memory for RDMA operations, each machine must register that memory with their RDMA NICs (RNICs) as an RDMA “memory region” (MR). During registration, the operating system reserves physical memory and ensures that the memory pages in their MRs are “pinned.” Mem-

## CHAPTER 2. BACKGROUND AND MOTIVATION

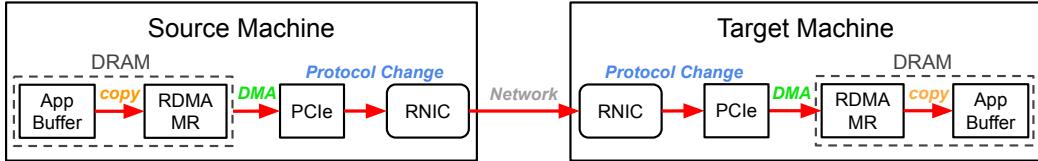

Figure 2.1: A high-level overview of data movement over RDMA. Data is first copied from the source machine’s application buffer to its RDMA memory region (MR). Next, the source machine’s RNIC transfers the memory from its DRAM to a PCIe channel utilizing DMA. The RNIC driver then converts the transaction to the appropriate network protocol (*e.g.*, InfiniBand). The data is then transferred over the network to the target machine, where all previous steps are executed in the reverse order until the data reaches the target machine’s application buffer.

ory pinning involves locking memory pages in physical memory so they cannot be swapped out by the operating system, ensuring the RNICs can reliably access them. Registration also involves translating virtual addresses to physical addresses and then registering them with the RNIC. Depending on the size and fragmentation of the memory, this registration process can take from microseconds to milliseconds, involving system calls and coordination between the CPU, OS, and hardware [96]. Frequent pinning introduces significant latency and increased CPU usage, greatly reducing the benefits of RDMA [76]. When an application is done with the MR, that region can be deregistered.

Several techniques have been developed to reduce the overhead of RDMA registration and deregistration, but also come with their own disadvantages and have limited applications [154]. For example, a commonly used technique is to pre-allocate and reuse MRs [76, 111, 150, 83]. Reusing MRs improves the overall performance of RDMA by avoiding de/registration overheads, but requires redundant data copies in the DRAM of both machines—thus adding some overhead and complexity. This is because data need to be copied from their original location on the source machine into a pre-allocated MR, and then from a pre-allocated MR on the target machine to its final destination.

The second RDMA issue is the inefficiency of data movement over RDMA. Figure 2.1 depicts a high-level overview of an RDMA operation using pre-allocated MRs on both machines. Three main issues contribute to the inefficiency: First, the data must be copied between the application buffers and MRs of both machines, resulting in redundant data and the overhead of the copy. Next, RDMA utilizes efficient DMA to transfer data to and from DRAM, but this requires at least two

## CHAPTER 2. BACKGROUND AND MOTIVATION

DMA transfers because transfers need to be performed by both RNICs. Lastly, transfers between PCIe-attached RNICs take place over a high-speed network (e.g., InfiniBand), introducing additional overheads from the required protocol/interface changes [45].

The third issue is that RDMA requires additional hardware and potential infrastructure changes. The initial investment of adopting RDMA can be prohibitively expensive due to the need for specialized RNICs and lossless network infrastructure [97]. While RDMA is often promoted for its low latency and reduced CPU usage, it still imposes some processing overhead and struggles with congestion control. Many of these challenges are addressed by using smart RNICs, which offload tasks from the CPU and optimize data flow. However, these advanced RNICs can even further increase costs, with prices reaching up to 5.7X more than commodity RNICs [112]. Integrating RDMA into existing infrastructures may also involve replacing traditional Ethernet networks, requiring significant system modifications. These investments make it challenging to identify appropriate applications and design systems that properly leverage RDMA performance gains to justify the initial expenses [103, 55, 48].

### 2.3 Compute Express Link (CXL)

Compute Express Link (CXL) is an open, industry-supported interconnect standard designed to provide high-performance, cache-coherent memory access between processors, memory expansion devices, and accelerators such as GPUs and FPGAs. CXL reduces overall system costs, simplifies software development, and minimizes access latencies by enabling resource sharing through an optimized data path, efficient coherency protocols, and minimizing redundant data copies [30].

CXL is built on the PCIe interface and defines three separate protocols for interacting with CXL devices:

- CXL.io: functionally equivalent to the PCIe protocol; it provides non-coherent load/store I/O access and is used for fundamental operations such as initialization, device discovery, and interrupts,

- CXL.cache: allows CXL devices to coherently access and cache host CPU memory, and

## CHAPTER 2. BACKGROUND AND MOTIVATION

- CXL.mem: allows the host CPU to coherently access CXL device memory for both volatile memory and persistent storage.

Furthermore, CXL devices are classified into three different types:

- Type 1 Devices: specialized accelerators that lack their own local memory (e.g., SmartNICs),

- Type 2 Devices: general-purpose accelerators such as GPUs and FPGAs with their own local DDR and/or HBM that provides coherent two-way access between host CPU memory and device memory, and

- Type 3 Devices: memory expansion devices that provide hosts access to disaggregated memory or byte-addressable persistent storage.

The first CXL Specification 1.0 was released in March 2019. It is based on PCIe 5.0 and allows hosts to coherently access the memory of directly attached accelerators and memory expansion devices [146]. CXL 1.1 was released in June 2019, comprising some errata and a new compliance chapter defining how interoperability testing between the host processor and an attached CXL device can be performed [119].

The next generation CXL 2.0 was released in November 2020, introducing single-level CXL switching, memory pooling, and CXL IDE (Integrity and Data Encryption) [31]. CXL 2.0 switches enable multiple hosts to connect to multiple CXL devices, either through a CXL switch or via direct connect. With CXL 2.0 memory pooling, CXL Type 3 memory expansion devices called multi-logical devices (MLDs) can be partitioned into logical devices (LDs), with up to 16 different hosts exclusively accessing the LDs of a single device.

CXL 3.0 doubles the bandwidth of CXL 2.0 up to 64 GT/s while maintaining the same latency, and introduces several new features that greatly differentiate it from traditional RDMA memory access. It implements memory sharing through an enhanced coherency protocol, replacing the bias-based coherency used in previous generations. This model enables snoop filter implementation and allows devices with their own memory to back-invalidate a host machine's cache. For example, Type 2 accelerators can fetch data from the host and save it in their own cache, perform work on the data, and then update the host's cache upon completion. This new coherency protocol also facilitates peer-to-peer connectivity between devices. CXL 3.0 devices are able to directly access each other's memory

without needing to go through the host, enabling a higher level of disaggregation and more flexible topologies.

CXL 3.0 also expands on memory pooling by introducing coherent memory sharing. With 2.0 memory pooling, Type 3 memory expansion devices can be partitioned to multiple hosts with each partition belonging to only a single host. In contrast, multiple hosts or devices can coherently access shared regions of memory with CXL 3.0 memory sharing. This feature gives us the opportunity to design systems that reduce unnecessary data movement and redundant data copies, resulting in less overhead and better resource utilization than RDMA.

## 2.4 Thesis Statement

This thesis proposal aims to utilize CXL shared memory to address three problems that stem from RDMA’s *migration-specific inefficiencies*: (1) the significant overhead of dirty-page tracking, which is required by traditional RDMA-based migration; (2) retransmission of pages that are dirtied after their initial copy, which increases both total migration time and the amount of data transferred; and (3) extended blackout periods during the stop-and-copy phase, with duration increasing as VM memory size grows.

To address these problems, we propose two CXL-based techniques that overcome fundamental limitations of state-of-the-art RDMA-based live VM migration. The first is a CXL-based migration approach that avoids dirty tracking and transfers each page only once, reducing the overhead of traditional multi-pass techniques. The second is a transparent CXL memory tiering migration strategy that dramatically reduces both the total migration time and data that needs to be migrated.

The goal of this work is to implement both techniques in QEMU, evaluate their performance against RDMA-based and hybrid migration approaches, and demonstrate that CXL migration and memory tiering can significantly reduce total migration time, blackout duration, and the amount of data transferred, particularly for large, memory-intensive VMs.

# Chapter 3

## Related Work

In this chapter, we survey related works about live migration algorithms, RDMA-based migration, shared-memory migration, and CXL remote memory and tiering.

### 3.1 Live Migration Algorithms

Clark *et al.* first proposed the standard pre-copy approach to live migration in 2005, in which memory pages are copied iteratively while the VM continues running. They showed that their prototype could migrate an 800 MB guest over 100 Mbps Ethernet in around 20–180 seconds while keeping blackout times between roughly 40–270 ms, depending on the workload [29]. Biswas *et al.* evaluated migration over 10 Gbps Ethernet and showed that transferring a 400 MB VM finishes in about 15 seconds with blackout times of approximately 300–400 ms [14]. More recently, in 2018 Google reported blackout times of around 50–200 ms for 30 GB VMs using 25 Gbps Ethernet, with total migration taking a few minutes [113]. These results demonstrate that even as network bandwidth improves, the effective speed of migration remains limited and blackout times show no improvement, underscoring fundamental limitations of traditional live-migration methods.

Researchers have proposed many techniques that make traditional migration more efficient. Ibrahim *et al.* add a stop-and-copy switch that adapts to memory-dirtying rate and link speed, cutting slowdown on HPC jobs by up to 10 $\times$  [61]. Haris *et al.* replace hand-tuned thresholds with a k-nearest-neighbor predictor that halts pre-copy once the predicted blackout meets an SLA, trimming total migration time by 86% and downtime by 65% [53]. Eswaran *et al.* preserve copy-on-write sharing among templated VMs during migration, cutting network

traffic by up to 92% and total migration time by 95% [39]. Liu *et al.* compress outgoing pages with Intel’s In-Memory Analytics Accelerator, achieving  $4.5\times$  compaction and restoring memory 55 percent faster with no extra CPU load [75]. Song *et al.* shard copy, checksum, and I/O across all cores and NIC queues, shrinking downtime by up to approximately  $280\times$  using 10 Gbps Ethernet [120]. Despite these optimizations, each technique still depends on dirty-page tracking and retransmitting dirtied pages, and therefore cannot fully eliminate the fundamental inefficiencies of traditional migration.

## 3.2 RDMA-Based Migration

State-of-the-art migration systems often utilize RDMA to reduce both migration time and CPU overhead. Huang *et al.* first demonstrated that InfiniBand RDMA can reduce total migration time by up to two orders of magnitude compared with TCP, inaugurating the zero-copy paradigm [59]. Follow-up work by Isci *et al.* recorded similar gains on enterprise traces while maintaining blackout under 200 ms [62]. Nomad snapshots RDMA queue pairs and restores them on a peer RNIC at the destination, enabling live migration of VMs with active RDMA connections [60]. Live migration over InfiniBand with single-root I/O virtualization (SR-IOV) support, which allows virtual machines to directly access virtual functions exposed by a physical NIC, achieves blackout times below 140 ms for 8 GB guests but requires device-specific coordination to transfer hardware state between source and destination [47].

While RDMA improves performance, it still relies on dirty-page tracking, retransmission of dirtied pages, and has architectural limitations (see Chapter 2.2). As a result, blackout times have seen little improvement and convergence remains slow under write-heavy workloads.

## 3.3 Shared Memory Migration

Researchers have begun to investigate shared memory as a more efficient alternative to network-based VM migration. Recent work by Grapentin *et al.* developed an IBM POWER9-based prototype that uses ThymesisFlow [105] to enable peer-to-peer, disaggregated memory access between servers. This work showed that key performance metrics from the perspective of applications running in the virtual machine, such as memory latency and throughput, were improved by up to

three orders of magnitude during the migration process [46]. Ran *et al.* evaluated migration using distributed shared memory (DSM), a system that allows multiple machines to share a unified memory space over a network. By preloading the VM’s memory into the DSM layer before hand-off, they reduced total migration time by about 70 percent [66]. Finally, we note that there was a BoF discussion about how CXL could be used for VM migration at the Linux Storage, Filesystem, Memory Management & BPF Summit in May 2023, along with a website titled "nil migration" [122]; however, no code has been released and there have been no updates on the website since. These works show that shared-memory migration is feasible on proprietary fabrics and motivate the development of CXL-based migration.

## 3.4 CXL Remote Memory and Tiering

Recent evaluations demonstrate that CXL 2.0 Type-3 memory-expansion devices achieve a significant portion of PCIe’s theoretical bandwidth, with latency about twice as high as local DRAM. Zhong *et al.* measure 97 ns idle latency for on-board DDR5 and 219 ns for a CXL device on Intel Sapphire Rapids, while per-core bandwidth tops out at 48 GB/s on an x16 PCIe 5.0 link [164]. Unal *et al.* report similar results in a HotOS 2025 study, measuring 112 ns latency for DRAM and 237 ns for CXL, with bandwidth just under 50 GB/s [134]. Weisgut *et al.* evaluate Micron CXL devices on Genoa servers and record a median 255 ns load latency together with 46 GB/s sustained copy bandwidth per device, scaling to 92 GB/s with four cards [145].

A recent survey by Sharma *et al.* thoroughly describes the architectural sources of CXL latency and bandwidth [32]. They state that CXL latency is composed of a protocol component and a queuing component, which depends on load. Protocol latency comes from two full traversals of the CXL port stack, each adding around 21–25 ns, plus approximately 15 ns of wire and retimer flight time, resulting in roughly 57 ns per memory access. Queueing latency is incurred only under load as requests pile up in the link-layer and memory-controller queues. Ultimately, this results in the average latency of CXL being roughly double that of local DRAM. As for bandwidth, 6–9% is lost to link-layer overheads, including bytes used for flit headers, CRC/FEC, SKP and ordered-set blocks, as well as flow-control bookkeeping based on credits.

Emerging research shows that CXL-attached DRAM can serve as a high-capacity second tier with only single-digit performance cost when guided by smart

### *CHAPTER 3. RELATED WORK*

hardware or OS policies. Transparent Page Placement (TPP) extends Linux NUMA balancing to demote cold pages to CXL and promote hot ones, keeping a tiered system within 1% of an all-DRAM baseline and outperforming stock Linux by up to 18% [92]. Intel Flat Memory Mode plus the Memstrata allocator moves tiering into the memory controller at cache-line granularity and enforces per-tenant isolation, keeping 82% of 115 Azure traces within 5% of local DRAM and trimming the worst slowdown from 34% to below 6% [164]. Nomad retains shadow copies and performs transactional page migration, cutting thrashing and delivering up to 6 $\times$  speed-ups over TPP under heavy memory pressure [151]. Alto introduces a memory-level parallelism-aware amortized off-core latency metric to suppress unnecessary migrations, improving performance by up to 12 $\times$  compared to TPP, Nomad, and two other policies across both NUMA and CXL hardware [86]. Together, these results paint an increasingly optimistic picture: CXL memory can reliably expand server capacity while keeping latency-sensitive workloads within a few percent of local DRAM performance.

# Chapter 4

## Desperately Seeking ... Optimal Multi-Tier Cache Configurations

Modern cache hierarchies are tangled webs of complexity. Multiple tiers of heterogeneous physical and virtual devices, with many configurable parameters, all contend to optimally serve swarms of requests between local and remote applications. The challenge of effectively designing these systems is exacerbated by continuous advances in hardware, firmware, innovation in cache eviction algorithms, and evolving workloads and access patterns. This rapidly expanding configuration space has made it costly and time-consuming to physically experiment with numerous cache configurations for even a single stable workload. Current cache evaluation techniques (*e.g.*, Miss Ratio Curves) are short-sighted: they analyze only a single tier of cache, focus primarily on performance, and fail to examine the critical relationships between metrics like throughput and monetary cost. Publicly available I/O cache simulators are also lacking: they can only simulate a fixed or limited number of cache tiers, are missing key features, or offer limited analyses.

It is our position that best practices in cache analysis should include the evaluation of multi-tier configurations, coupled with more comprehensive metrics that reveal critical design trade-offs, especially monetary costs. We are developing an  $n$ -level I/O cache simulator that is general enough to model any cache hierarchy, captures many metrics, provides a robust set of analysis features, and is easily extendable to facilitate experimental research or production level provisioning. To demonstrate the value of our proposed metrics and simulator, we extended an existing cache simulator (PyMimircache). We present several interesting and counter-intuitive results in this paper.

## 4.1 Introduction

The vast configuration space of multi-tier caching enables the design of very complex systems. Several tiers of cache and persistent storage can be allocated in numerous arrangements. Moreover, devices can be partitioned into many differently sized cache segments for separate applications. All of these devices can be implemented within, and interact with, any number of independent, large-scale infrastructures (*e.g.*, cloud services, virtual machines, big data warehouses, distributed systems). Furthermore, new storage technologies are constantly emerging (*e.g.*, NVM, 3D flash), introducing additional complexity, greater capacities, and different cost/performance profiles. Our ability to dynamically change hardware in live systems (*e.g.*, adding or deleting RAM, SSD, NVM) has also been increasing, particularly in cloud environments and virtual machines [49, 27, 28], making it significantly easier to reconfigure a cache hierarchy. Workloads continue to evolve as well, with complex and diverse access patterns that affect the frequency of data reuse and the size of working sets, two of the most influential factors in any caching system [121, 147, 116, 10, 24].

Research in cache algorithms and policies is also trying to keep up with these changes. Machine learning and similar techniques that leverage historical data are being incorporated into caching systems to bolster prefetching [156], dynamically switch between replacement algorithms [114, 139, 116], or enhance existing eviction policies [5]. I/O classification has been used to enforce caching policies and improve file system performance [95]. Multi-tier cache eviction algorithms that are aware of some or all layers in the hierarchy at any given time are being developed [24]. The challenges of cache resource allocation and provisioning are being investigated as well [71, 13]. Zhang *et al.* introduced CHOPT, a choice-aware, optimal, offline algorithm for data placement in multi-tier systems [160]. Algorithms such as CHOPT are promising solutions for efficiently finding optimal multi-tier configurations, but their bounding assumptions and inability to model all parameters limit the configuration space they can explore.

Physically experimenting with various cache configurations is costly and time-consuming, with so many parameters to consider (*e.g.*, number of tiers, device types and models, caching policies). A well-known technique for evaluating cache performance without running experiments is Miss Ratio Curve (MRC) analysis [141, 54, 15, 58]. MRCs plot the cumulative miss ratio of all requests in a given workload for some cache eviction algorithm(s) as a function of cache size. Cache size usually ranges from one data block to the size required to store every unique block accessed in the workload, also known as the *working set*. This technique

## CHAPTER 4. DESPERATELY SEEKING ... OPTIMAL MULTI-TIER CACHE CONFIGURATIONS

has many uses, such as comparing eviction algorithms' performance for a given workload or identifying optimal cache size allocations. However, MRCs evaluate the performance of only a single cache and are not capable of accurately modeling the complicated interactions between devices in a multi-tier cache. Recent studies have shown that traditional MRCs are even sub-optimal for resource allocation in a single layer, since they admit data with poor locality into the cache. [41].

It is vital that our methods of evaluating caches mature as storage technologies and cache hierarchies continuously evolve. For example, examining performance metrics such as latency or using an MRC to analyze miss ratio as cache size increases may be misleading without also considering the monetary cost of purchasing and using the cache. Cost has a non-linear, positive correlation with cache size, and is fundamentally the primary constraint when deciding how much cache to include in a system. If this were not the case, everyone would cache all data in copious amounts of the fastest DRAM money can buy and back it up with a huge battery. Furthermore, improved performance does not directly translate into cost efficiency, especially in a multi-tier system where devices' cost and performance characteristics can vary wildly. The purchase cost of hardware is a simple example. Ideally, we should be evaluating more comprehensive metrics such as the total cost of ownership, which combines other metrics such as power consumption, the cost of labor to maintain a system, and the projected lifetime of devices given access patterns. It is also essential that we can freely evaluate the relationship between metrics (e.g., throughput/\$) so we can make educated design decisions with full awareness of the inherent trade-offs.

The most complete solution would be an  $n$ -level I/O cache simulator that could quickly and accurately evaluate many configurations. While there are some advanced CPU cache simulators available [63, 35, 104, 143, 91], storage cache simulators are scarce and lacking. State-of-the-art storage cache simulators are mostly outdated; they either can simulate only a single layer or some fixed set of layers, have limited analysis features, are not easily extendable, or are simply not released to the public [148, 51, 1]. PyMimircache [155] is a popular open-source storage simulator with several useful features that is actively maintained. However, even this simulator is inadequate; it also can simulate only a single layer of cache with no implementation of back-end storage, has no concept of write policy, and its analysis features are limited. The main strength of PyMimircache is its ability to perform MRC analysis on multiple cache replacement algorithms.

It is our position that best practices in cache research need to be broadened to reflect the growing multi-tier configuration space. This paper makes the following contributions:

## CHAPTER 4. DESPERATELY SEEKING ... OPTIMAL MULTI-TIER CACHE CONFIGURATIONS

1. We explore current trends in cache analysis and propose that best practices in cache research including the analysis of multi-tier configurations and a more comprehensive set of evaluation metrics (*e.g.*, monetary cost).

2. We describe the critical features an  $n$ -level I/O cache simulator should have and outline the design of a simulator we began to develop.

3. We extended PyMimircache to function as a multi-tier cache simulator, experimented with many configurations on a diverse set of real-world traces, and present initial results that support our position.

### 4.2 Cache Analysis

The fundamental strategy in engineering a cache hierarchy involves placing faster and typically lower-capacity devices in front of slower devices to improve the overall latency of accessing frequently reused data. There is a tangible dollar cost per byte increase when purchasing hardware with better performance attributes. Therefore, it follows that the cache size and speed are closely correlated with the purchase cost. Straightforward logic dictates that performance is constrained by cost, so unless money is in endless supply, the best practice should be to evaluate these metrics together. Surprisingly though, cost is often overlooked during analysis in favor of performance metrics such as raw throughput, latency, or hit/miss ratio [144, 27, 24, 109, 41, 23, 19].

The argument can be made that any improvement in cache performance translates into a reduction in cost when designing a cache, such that the relationship between cost and performance does not necessarily need to be considered. This is situationally true, particularly when evaluating performance in a single-tier caching system. However, in a more realistic, multi-tier storage or CPU cache hierarchy, the large configuration space and complex interactions between tiers produce scenarios where the relative performance per dollar between two configurations is vastly different, necessitating a more complex analysis (see Section 4.4 for examples).

Performance metrics have long been the standard in cache analysis. Recently, additional metrics that are more relevant and informative for specific applications have gained popularity in storage research. The 95<sup>th</sup> (P95) or 99<sup>th</sup> (P99) percentile latency, often referred to as *tail latency*, is an important quality of service (QoS) metric for cloud [153, 125] and web [64, 34, 52, 13] services, as well as at the hardware level [77, 18, 82, 36]. Inter-cache traffic analysis has been used to design

more efficient cache hierarchies in modern microprocessors [102]. Reducing the energy consumption of storage systems is beneficial for the environment, lowers operation costs, and promotes advancements in hardware design [20, 80, 118, 137]. Even the total cost of ownership (TCO) can be difficult to calculate when considering all the factors that contribute to capital and operational expenditures (CapEx and OpEx) [81, 79].

It is our position that cache analysis should be conducted using a diverse set of metrics whenever possible. These metrics should be evaluated at various level of granularity: at each individual layer, some subset of layers, or globally. Moreover, we need to create complex metrics (*e.g.*, throughput/\$) that allow for analysis of their informative relationships and reveals critical design trade-offs.

### 4.3 Multi-tier Cache Simulation

**Simulator Design** A general,  $n$ -level I/O cache simulator with a rich set of features is necessary to thoroughly explore the multi-tier caching configuration space and analyze our proposed metrics. We are developing such a simulator that includes (but is not limited to) the following capabilities: **(1)** *Write policy* that determines where data is placed upon write requests. We will support traditional write policies (*e.g.*, write through, write back, write around), but also allow user-defined policies. **(2)** *Admission policy* that controls if and how data is promoted and demoted throughout the hierarchy by request size, address space, or simply whether layers are inclusive or exclusive of each other. **(3)** *Eviction policy* that decides which data to evict when a cache is full and new data needs to be brought in. There will be support for single-layer or global policies, as well as the ability to easily add new policies. **(4)** *Trace sampling* techniques (*e.g.*, Miniature Simulations [142]) that reduce the size of a trace to greatly decrease simulation time while maintaining similar cache behavior. **(5)** *Prefetching* to retrieve data before it is requested with techniques like MITHRIL [157] that exploit historical access patterns.

The associated API will fully expose all data structures at request-level granularity or for any given real timestamp or virtual ones (where the trace has only ordered records without their original timing). This will allow users to perform important analysis such as examining clean and dirty pages at any level, measure inter-reference recency, calculate stack distance metrics when relevant, or perform any type of analysis offered by our simulation framework on a subset of a trace. The simulator will also be coupled with modern visualization tools that enable

## CHAPTER 4. DESPERATELY SEEKING ... OPTIMAL MULTI-TIER CACHE CONFIGURATIONS

users to efficiently explore the large amount of data it produces.

**Multi-tier Cache Reconfiguration** A major motivation for simulation is seeking optimal cache configurations. However, efficiently reconfiguring a multi-tier cache hierarchy is another challenging problem. In this work, we analyze various physical devices for simplicity, but manually swapping out devices is often not a feasible solution. More likely, multi-tier caches may be dynamically reconfigured in cloud, distributed, and virtual environments, where storage can more easily be allocated through virtualization abstractions. For example, distributed memory caching systems (*e.g.*, Memcached) can greatly benefit from automatically reconfiguring cache nodes in response to changes in workload; but this process can significantly degrade performance as nodes are retired and data is migrated. Hafeez *et al.* developed EIMem, an elastic Memcached system that uses a novel cache-merging algorithm to optimize data migration between nodes during reconfiguration [50]. Moving between configurations in any caching system has a *temporarily* negative impact on performance, until the new caches are fully warmed [166, 22]. Therefore, efficient reconfiguration methods are essential to fully leverage any techniques that find optimal configurations (including simulations).

**PyMimircache Extension** To demonstrate the utility of our proposed simulator, we extended PyMimircache [155], a storage cache simulator with an easily extendable Python front-end and efficient C back-end. We made several simplifying assumptions for this extension and experimented with a subset of the possible features we are proposing. **(1)** We implemented a traditional write-through policy and an “optimistic” write-back policy as global write policies. The write-through policy is consistent and reliable: a block is written to every cache layer and the back-end storage whenever there is a write request. Our write-back policy is optimistic: it only writes to the first layer and assumes this data will be flushed to persistent storage at some point in time, outside of the critical path where it does not affect performance (*i.e.*, we do not account for the write in any other layer). This simplified version of write-back models the best-case performance scenario, which we found useful for exploring the potential effects of write policy. A more realistic write-back would require asynchronous functionality that is not available in PyMimircache, and is a limitation of this work. **(2)** All evicted blocks are discarded rather than demoted (moved or copied) to some lower layer of cache or back-end storage. **(3)** Layers of DRAM are included in our simulations even

## CHAPTER 4. DESPERATELY SEEKING ... OPTIMAL MULTI-TIER CACHE CONFIGURATIONS

though we are using block traces, which capture requests for data that was not found in DRAM. This is a limitation of the traces we are using; the simulator we implement will be able to operate on any data item from any trace that includes some form of address accesses. The simulator will support traces obtained from networks (*e.g.*, NFS, HTML), distributed systems (*e.g.*, HPC, Memcached), system calls, block traces, and potentially more. **(4)** Throughput is limited by the system where traces were actually captured since we experiment with block traces. For demonstration purposes, we ignore this limitation and assume requests are fed as fast as possible without using the original request timestamps. This allows us to show how we can potentially evaluate throughput when using different hardware configurations. **(5)** We consider each layer to have a portion of its capacity partitioned for caching to emulate various cache sizes at each layer using the specifications of a single device.

A high-level description of how we extended PyMimircache is as follows: **(1)** We feed an original block I/O trace to an instance of PyMimircache, this is the top layer (“L1”) of our cache hierarchy. **(2)** This instance generates two output files: i) A log file “L1-log” containing counters for the following: read hits, write hits, read misses, write misses, data read, data written. ii) We specify a new trace file called “L1-trace” which contains read requests that missed in L1, as well as all write requests. As per our assumptions, write requests are not included when using write-back policy and evicted blocks from L1 are never included. These intermediate trace files are stored in memory using Python-based virtual files to avoid disk I/O costs. **(3)** After the L1 instance of PyMimircache completes, we feed the generated “L1-trace” from step 2 as input into another, separate instance of PyMimircache. This emulates our L2 layer. **(4)** We repeat steps 2–3 for L2, L3, etc. **(5)** When all layers have been processed, we aggregate all the log data into a single log file for that experiment. **(6)** We have a higher-level script that we pass parameters to for each layer’s device: purchase cost, capacity, and average read and write latencies. This script records and calculates the following metrics for the cache configuration of an experiment: total purchase cost, partitioned device capacities, miss ratio per layer, and total read and write latency incurred. It can be [re]run at any time using previously obtained simulation logs, and is separate from the actual simulation process.

## 4.4 Evaluation

**Workloads** In this section, we evaluate simulation results gathered using the Microsoft Research (MSR) traces. These 36 traces, each about a week long, were collected from 36 different volumes on 13 production servers at MSR in Cambridge, Massachusetts, as described in detail by Narayanan *et al.* [99]. The percentage of total requests that access unique blocks (*i.e.*, data used for the first time) in these traces range from 1% to 97%, which is representative of the frequency of data reuse. The percentage of total requests that are writes range from nearly 0% to almost 100%, and is ideal for evaluating the effects of write policies.

We are continuing to run additional experiments using 9 traces from the Department of Computer Science at Florida International University (FIU) [137] and 106 traces from CloudPhysics [141], but do not present results here due to space limitations.

**Experimental setup** We ran simulations on the MSR traces using between 1 and 3 layers of cache, in addition to the back-end storage device. Each simulation consisted of a configuration of several parameters: cache and back-end sizes, eviction algorithms, and global write policy. The capacity required to hold the entire working set of a trace dictated the cache and back-end storage sizes for every configuration. The back-end size was always fixed to be the same size as the working set, since the data initially resides in the back-end. The cache sizes selected for the first layer of cache are 100 evenly spaced sizes between 1 block (512 bytes) and the size of the working set for that trace. 100 is the default number of points for plotting MRCs with PyMimircache. The second and third layers of cache are 10 evenly spaced sizes within the same range. Using 10 cache sizes for these layers rather than 100 drastically reduced the time required to complete each experiment while still revealing the entire range of metrics (albeit with fewer data points within that range).

In this work, we only present results for configurations using a Least Recently Used (LRU) eviction policy at every layer, although we are varying these policies in our ongoing simulations. We simulated each of the MSR traces using our extension of PyMimircache (see Section 4.3) and then calculated cost and performance metrics using the device specifications described in Table 4.1.

While these comprehensive traces represent a wide variety of workloads, they have only a relatively small working-set size that can easily fit in a modern server’s RAM. Therefore, to simulate larger workloads (*e.g.*, bigdata, HPC), we treat the original MSR traces as if they were scaled-down spatial samples of larger traces.

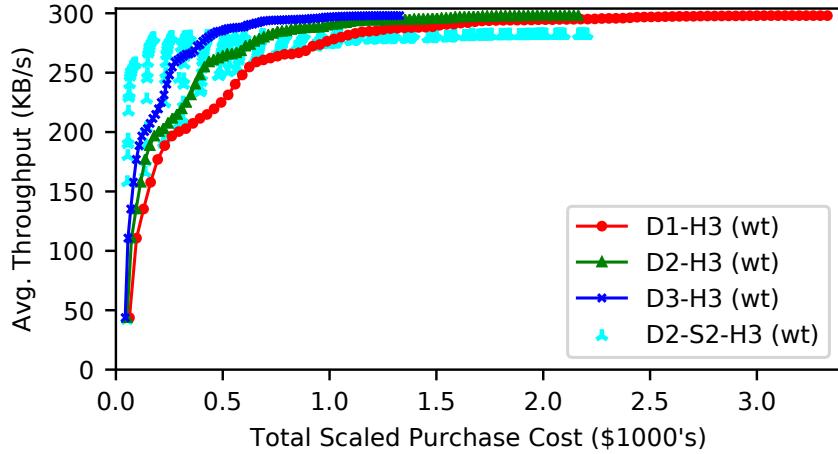

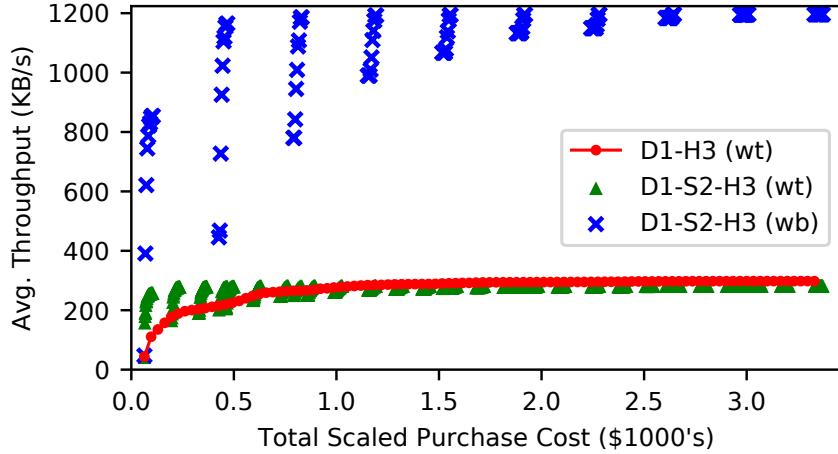

Figure 4.1: Effects of an intermediate SSD tier (Workload MSR hm-1)

We call this technique *reverse-mini-sim*: the reverse of the miniature simulations technique for down-scaling traces introduced by Waldspurger *et al.* [142]. Miniature simulations was shown to be fairly accurate at a sampling rate of 0.001 on the MSR traces, so we multiply the purchase cost (X axis) by a factor of 1,000 times: this simulates a workload whose working set size is  $1,000 \times$  larger.

Each data point in our figures represents a configuration with some set of cache sizes. We assume that each layer consists of an independent device with a portion of its capacity partitioned for caching and the remaining capacity as unused. For example, a cyan triangle in Figure 4.1 at Total Scaled Purchase Cost of around \$235 represents the average throughput of all requests in a single simulation of the hm-1 trace with an L1 LRU cache of 61,865 blocks partitioned in device D2, an L2 LRU cache of 199,344 blocks partitioned in device S2, and back-end storage of device H3 partitioned to fit the working set of 687,396 blocks.

**Cache hierarchy depth** Figure 4.1 shows (D1-H3, red) that too little RAM hurts performance but too much wastes money. Adding a bit of SSD cache (D2-S2-H3, cyan) between DRAM and HDD (D2-H3, green) can help, but *not* always (some cyan dots are *below* the green line). Consider the knee of D1-H3 (around X=\$500): there are D2-S2-H3 configurations that provide higher throughput for the same cost, same throughput for less cost, and even *both* higher throughput and less cost. Surprisingly, we also see that purchasing more of a cheaper DRAM (D3-

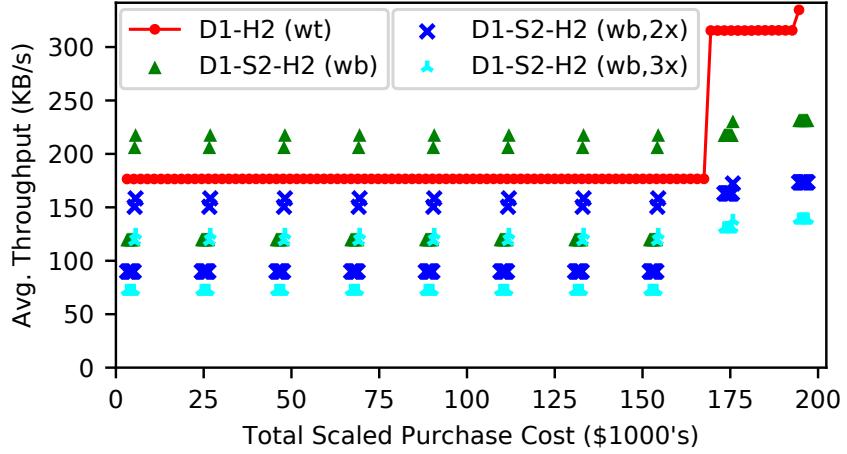

Figure 4.2: SSD Aging Effects (Workload MSR src2-1). 2 $\times$  and 3 $\times$  indicate configurations where S2 has 2–3 $\times$  increased latency due to the potential effects of SSD aging

H3, blue) for the same cost of a more expensive DRAM (D1-H3) yields overall better performance. Therefore, we can sacrifice DRAM performance for a larger amount of DRAM to get better results.

**Solid-state drive (SSD) degradation** Storage devices have an expected lifetime which is typically defined by some amount of I/O. For example, it is well-known that the memory cells within SSDs can only be written to a finite number of times before they are no longer usable [65, 88, 101]. While the lifespan of devices is a parameter that should be considered when estimating the total cost of ownership of a storage system over some period of time, it is also important to evaluate the performance impact this aging process can have. Studies have shown that SSD aging can increase average latency by around 2–3 $\times$  [67]. To simulate this effect, we multiplied the latency specifications of device S2 and analyzed the results alongside simulations using its original specifications. Figure 4.2 shows that while a new SSD (D1-S2-H2, green triangles) improves performance when inserted into a D1-H2 tier (red), when the SSD is aged (blue and cyan), performance is actually worse than not having the SSD at all. For users with write-heavy workloads or infrastructures where these devices are expected to receive a lot of I/O traffic over a short period of time, choosing to exclude SSDs completely may not only save

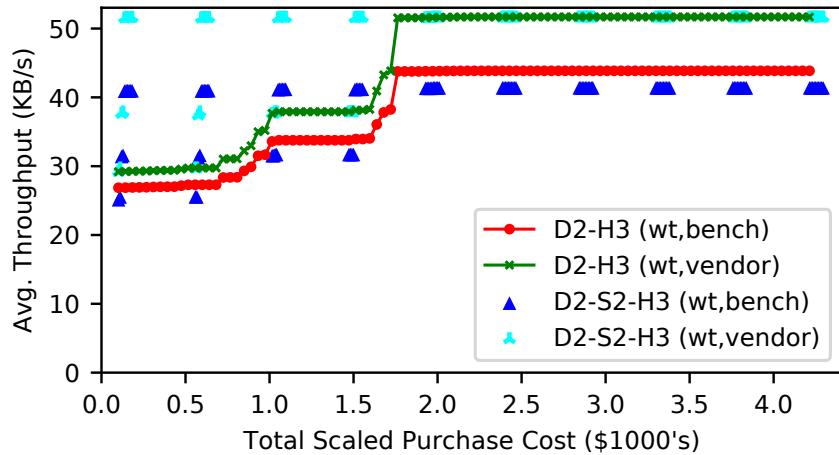

Figure 4.3: Variation between vendor-reported specs and independently operated benchmarks (Workload MSR web-3)

money, but also yield a similar or better average throughput over time.

**Device specification variance** Storage vendors want to convince consumers that their latest device is competitive. They do so by publishing many device specifications: storage capacity, physical dimensions, hardware interface, durability, energy consumption, and performance metrics. While most specifications are fairly standard, a wide variation of performance metrics can be found, even amongst the same type of device and vendor. Some commonly found metrics are the minimum, average, median, or maximum values for latency, bandwidth, or throughput. These metrics may also be further refined as random or sequential workloads, or separated by reads and writes. These measurements are obtained via benchmarks using some specific workload(s), software environment, and hardware configuration, which are sometimes disclosed at varying levels of detail. This poses a significant problem for consumers, who often are unable to reproduce vendors' performance results. Given such a vast configuration space of variables that can affect performance and the understandable motivation for vendors to publish optimistic results, how can storage devices be reliably compared for their own usage? A handful of independent, reputable websites have emerged by fixing these variables and benchmarking devices from different vendors, and producing realistic, trustworthy specifications: AnandTech [6], Tom's

Figure 4.4: Write-through vs. Write-back policy effects (Workload MSR hm-1)

Hardware [131] and UserBenchmark [135].

In this experiment we show the difference between numbers reported by vendors and others. Figure 4.3 shows that inserting an SSD tier between DRAM and HDD provides equal or better performance when using vendor reported specifications (green and cyan). However, specifications obtained from Anandtech [6] (red and blue) show that the majority of the configurations yield worse average throughput.

**Write Policy** The write policy of a cache hierarchy determines how and where data is written whenever there is a write request. Write-through policy ensures data consistency by writing data to every cache and storage device in the hierarchy. However, this incurs the write latency of every device and negatively impacts overall performance. The write-back policy improves performance over write-through by only writing to the cache and then flushing data to back-end storage at a more favorable time. The downside of write-back is that data is at risk of being lost in the event that a cache device fails or whole system loses power. If reliability is more important, a write-through policy is the obvious choice, but how much impact will this have on performance? Figure 4.4 compares write-through and write-back policies (policy implementations described in Section 4.3). Using an optimistic write-back (wb) policy we achieve up to  $6\times$  better throughput for the same cost as write-through (wt) with the same devices. Note that a more accurate

*CHAPTER 4. DESPERATELY SEEKING ... OPTIMAL MULTI-TIER CACHE CONFIGURATIONS*

write-back policy will account for the delayed writes, which will tie up the storage devices even during idle times.

## 4.5 Conclusion

Designing and evaluating cache hierarchies has become incredibly complex due to the expanding multi-tier configuration space. In this work, we analyzed the deficiencies of single-tier cache analysis and common cache evaluation metrics. We propose that best practices in cache research should include the analysis of multi-tier systems, as well as the evaluation of a more comprehensive set of metrics (particularly monetary cost) and their relationships. We are developing an  $n$ -level I/O cache simulator with a rich set of features and analysis tools that is capable of modeling any cache hierarchy. We extended PyMimircache to function as a multi-tier cache simulator and experimented with a wide variety of workload. We presented interesting and counter-intuitive results that demonstrate the need for our proposed simulator and multi-tier analysis.

*CHAPTER 4. DESPERATELY SEEKING ... OPTIMAL MULTI-TIER CACHE CONFIGURATIONS*

| <b>ID</b> | <b>Device</b>                           | <b>Type</b> | <b>Price</b> | <b>Capacity</b> | <b>Average Latency (Benchmark Source)</b>                                                                      |

|-----------|-----------------------------------------|-------------|--------------|-----------------|----------------------------------------------------------------------------------------------------------------|

| D1        | G. Skill TridentZ DDR4 3600 MHz C17     | DRAM        | \$150        | 16GB            | 0.0585 $\mu$ s r/w (UserBenchmark)                                                                             |

| D2        | G. Skill TridentZ DDR4 3000 MHz C15     | DRAM        | \$97         | 16GB            | 0.0642 $\mu$ s r/w (UserBenchmark)<br>0.01 $\mu$ s r/w (Vendor)                                                |

| D3        | Corsair Vengeance LPX DDR4 2666 MHz C16 | DRAM        | \$59         | 16GB            | 0.0726 $\mu$ s r/w (UserBenchmark)                                                                             |

| S2        | HP EX920 M.2 NVMe                       | SSD         | \$118        | 1TB             | 292 $\mu$ s read<br>1,138 $\mu$ s write (AnandTech)<br>20 $\mu$ s read<br>22 $\mu$ s write (Vendor)            |

| H2        | WD Black 7200 RPM                       | HDD         | \$60         | 1TB             | 2,857 $\mu$ s read<br>12,243 $\mu$ s write (AnandTech)                                                         |

| H3        | Toshiba MK7559GSXP                      | HDD         | \$65         | 750GB           | 17,000 $\mu$ s read<br>22,600 $\mu$ s write (Tom's HW)<br>17,550 $\mu$ s read<br>17,550 $\mu$ s write (Vendor) |

Table 4.1: Device specifications and parameters. Each device is denoted with a letter and number for brevity (1 is high-end, 2 is mid-range, and 3 is low-end). Devices S1, S3, and H1 are skipped for space considerations. Prices were obtained from Amazon in September 2019. Benchmarked specifications were correlated from device vendors, AnandTech [6], Tom's Hardware [131], and UserBenchmark [135].

# Chapter 5

## Accelerating Multi-Tier Storage Cache Simulations Using Knee Detection

Storage cache hierarchies include diverse topologies, assorted parameters and policies, and devices with varied performance characteristics. Simulation enables efficient exploration of their configuration space while avoiding expensive physical experiments. Miss Ratio Curves (MRCs) efficiently characterize the performance of a cache over a range of cache sizes, revealing “key points” for cache simulation, such as knees in the curve that immediately follow sharp cliffs. Unfortunately, there are no automated techniques for efficiently finding key points in MRCs, and the cross-application of existing knee-detection algorithms yields inaccurate results.

We present a multi-stage framework that identifies key points in *any* MRC, for both stack-based (*e.g.*, LRU) and more sophisticated eviction algorithms (*e.g.*, ARC). Our approach quickly locates candidates using efficient hash-based sampling, curve simplification, knee detection, and novel post-processing filters. We introduce *Z-Method*, a new multi-knee detection algorithm that employs statistical outlier detection to choose promising points robustly and efficiently.

We evaluated our framework against seven other knee-detection algorithms, identifying key points in multi-tier MRCs with both ARC and LRU policies for 106 diverse real-world workloads. Compared to naïve approaches, our framework reduced the total number of points needed to accurately identify the best two-tier cache hierarchies by an average factor of approximately 5.5× for ARC and 7.7× for LRU.

## CHAPTER 5. ACCELERATING MULTI-TIER STORAGE CACHE SIMULATIONS USING KNEE DETECTION

We also show how our framework can be used to seed the initial population for evolutionary algorithms. We ran 32,616 experiments requiring over three million cache simulations, on 151 samples, from three datasets, using a diverse set of population initialization techniques, evolutionary algorithms, knee-detection algorithms, cache replacement algorithms, and stopping criteria. Our results showed an overall acceleration rate of 34% across all configurations.

### 5.1 Introduction

A cache’s miss ratio is one of the most important predictors of its performance. A miss-ratio curve (MRC) for a given cache and replacement algorithm plots the cumulative miss ratio for all accesses as a function of the cache size, providing a powerful tool for analyzing the performance of live systems and dynamically adjusting cache configurations as workload conditions change [142, 13]. MRCs can also inform offline evaluations such as comparing caching algorithms or analyzing monetary cost vs. storage-system performance [38].